基板の層構成を決め、設計規則を適用する

基板の層数や仕様は、製造コストや製造歩留まりなどに大きな影響を及ぼします。また、電気特性にも関わるため、設計開始前に関係者で話し合う必要があります。決定する基準になる項目を知ることも重要です。

層数と層構成設定

基板の外形や制限領域、配線情報、配置すべき部品の種類と数が決まった後、基板の層数の見積もりに入ります。ここでは層構成も決めます。基板外形とともに基板の層数があらかじめ規定されている場合もあります。

基板の層数や層構成は、特性インピーダンスなど配線の電気特性や基板の総厚さ、製造コストや製造歩留まりなど多くの要素が関係します。このため、基板設計者が独断で決定することはできません。

通常、基板設計者は信号配線に必要な層数を要求し、その必要配線層数を基に、配線の電気特性やその他の条件から層構成を決定します。基板設計者は、このようにして決まった層構成をCADの基板データに入力したり、ライブラリの層構成を読み込んだりします。

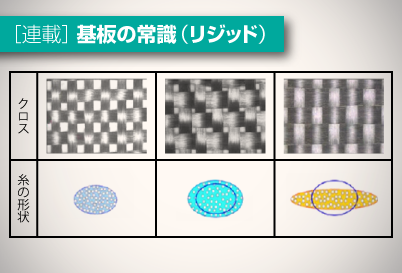

配線層数は幾つかの条件から決定します。最も重要な条件は配線幅、パッドと配線の間隙、配線と配線の間隙です。これらの条件は、製造歩留まりと配線の電気特性から決めます。通常は幾つかの数値が標準として決められています。

使用するビアの径も重要な要素です。特にIVH(Interstitial Via Hole:非貫通ビア)やB/B(Blind/Buried)ビアを使うか使わないかは、層数決定に大きな影響があります。これも、板厚や製造難易度によって何種類か決められています。

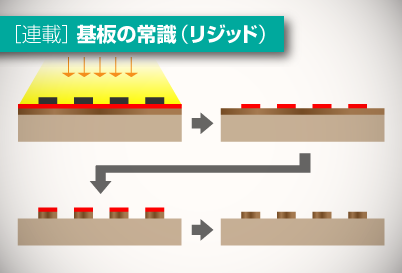

ビルドアップ構造を採用するか否か。採用する場合、ビルドアップ層を何層にするかも大きな問題点です。

ビルドアップ層では、線幅や配線間隙を小さくでき配線密度は高まりますが、コストも上昇します。ビルドアップ構造を使って層数を減らすか、通常の基板構造で層数を増やすのかは、トータルの板厚、電気特性、コストなど、多くの要因を考えて決定します。

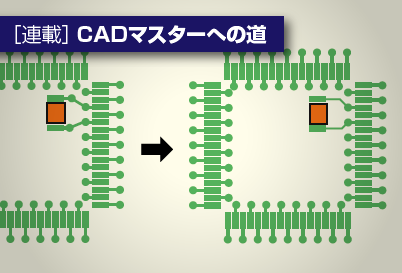

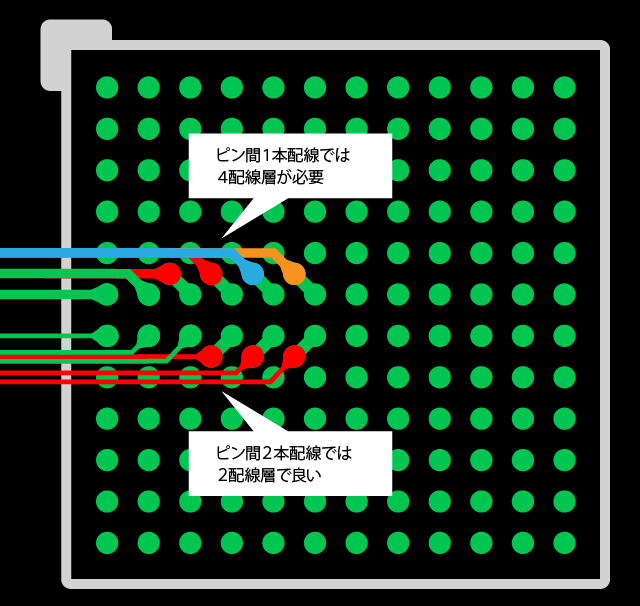

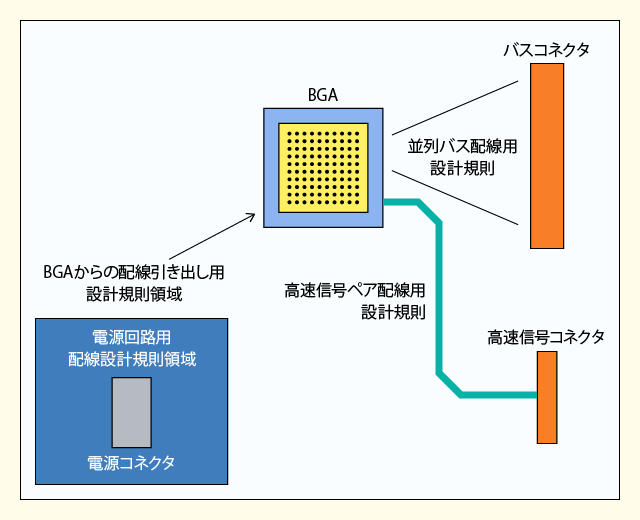

通常、BGAや高密度コネクタのように、ピン数の多い部品のピンから全ての配線を引き出す部分に、最も多くの配線層が必要になります(図1)。

使用部品を検討して、最も配線の引き出しが困難な部品に対して、幾つかの条件での配線必要層数を算出して、レポートします。

図1. BGAの引き出し配線が層数を決める

図1. BGAの引き出し配線が層数を決める

伝送線路解析には追加情報が必要

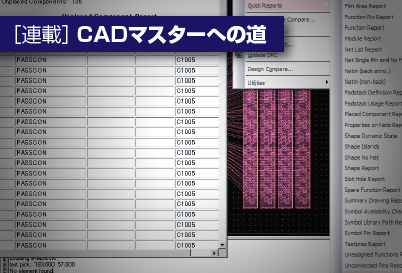

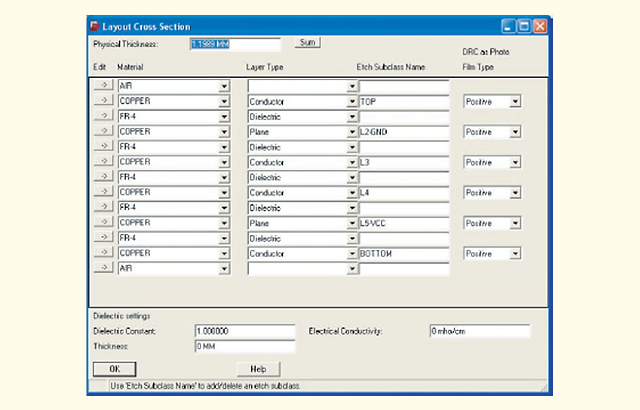

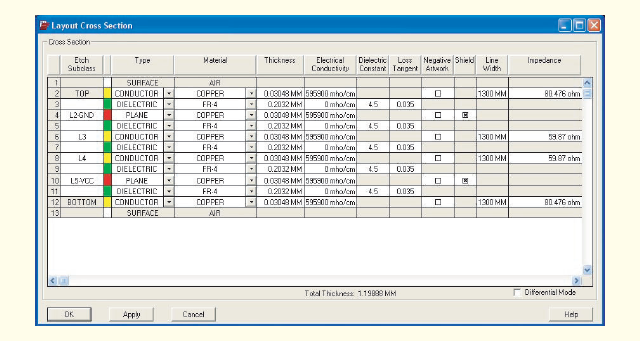

基板レイアウトには基板の層構成の順番情報が必要なものの、絶縁層の材質や厚さは必要ありません(図2)。しかし、伝送線路解析には材料の電気的特性や厚さ情報が必要です(図3)。

図2. レイアウトCADの層構成画面

図2. レイアウトCADの層構成画面

図3. 伝送線路シミュレーターの層構成画面

図3. 伝送線路シミュレーターの層構成画面

一般の基板設計CADでは、3次元方向のデータとして層の構成順番だけのデータや単純な層の厚さだけの情報を持っています。これが2.5次元と呼ばれるゆえんです。一部のCADでは、ビアや配線層の相互の関係、部品配置の状況などを見やすくするために3次元の機能をサポートしているものもあります。

3次元の機構設計CADにデータを出力する機能を持ち、3次元CADとして基板や部品の3次元画像を見たり、3次元解析ができるようにした基板設計CADシステムもあります。一部のEMI解析などでは、3次元情報を使って精度の高い電磁界解析をするものもあります。

今後、基板設計CADでも3次元データ化が少しずつ進んでゆくものと思われます。

設計規則の入力

一般に配線幅や配線と配線の間隙、配線と部品パッドの間隙などの配線設計規則は、層構成が決まる前にある程度決定しています。最終的には層の構成と一体で詳細な条件を決定します。

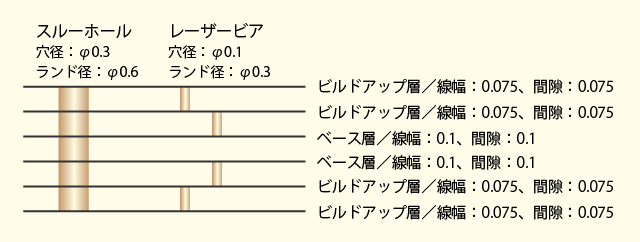

設計規則は製造歩留まりから考えて、部品面とはんだ面の表面層と内層信号層、内層プレーン層ではそれぞれ異なるのが普通です。 ビルドアップ基板の場合、当然、ビルドアップ層とコア層では、配線規則や使用するビアの径、ビアの設計規則など大きな違いがあります。さらにUL規格では、高電圧信号と低電圧信号で異なる設計規則を要求しています。

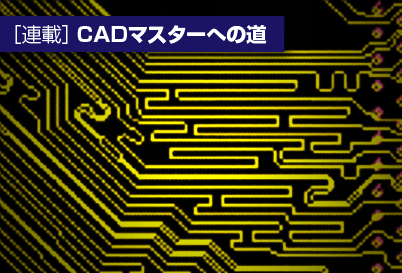

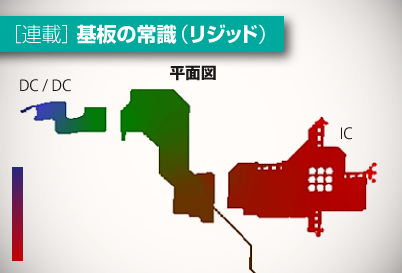

加えて電気的な特性から、高速信号と一般信号、アナログ信号領域とデジタル信号領域、電源信号など、基板上の領域や信号ごとに異なる配線幅や配線間隙など、異なる設計規則を適用する場合が一般的です(図4、図5)。

図4. 基板の領域や信号によって配線規則が異なる

図4. 基板の領域や信号によって配線規則が異なる

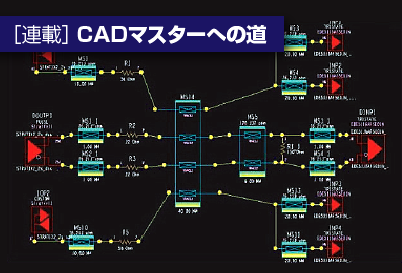

図5. 基板の層によって配線規則やビアが異なる一例

図5. 基板の層によって配線規則やビアが異なる一例

高速信号では、低電圧の差動データ伝送方式が多く採用されています。この差動信号では、ペア配線間の遅延誤差に対する要求が特に厳しく、差動ペア配線間だけの特別な設計規則が必要になります。

BGAなど高密度狭ピンピッチの部品では、配線の引き出しが難しいので、引き出しに必要な部分だけ設計規則を変更して、基板の層数を減らす工夫をする必要があります。場合によっては、部品パッドに直接ビアを打つことを許す場合もあります。このように、部品に依存した設計規則もあります。

CADの助けを借りて設計規則を設定する

CADでは、この設計規則を基に、基板設計やチェックを進めます。

このように設計規則は複雑です。それでも、製造歩留まりが高く、層数が少なく特性の安定した基板を設計するためには、正確な値を間違いなく設定する必要があります。

このため、各CADシステムはスプレッドシート形式を使ったり、専用の入力テーブルを用いたり、規則のライブラリ化を図ったりして、複雑な設計規則の入力を間違いなく簡単に行えるように工夫しています。

また、この基本的な設計規則と、配線の制約条件は一部、区分けができなかったり、重複したりしています。このため、複数の方法で同じような設定ができたり、似たような設定なのに細かいところが異なる設定がある場合があります。

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。