配線幅と間隔

配線幅と間隔を決定する際、まずどのような配線かを考えることが必要です。ここでは、大きく3つの要素に分けて説明します。

・一般信号配線

・インピーダンス指定配線

・大電流配線

一般信号配線

一般信号配線の配線幅と間隔は、一般的に安価に製造できる最小の配線幅と間隔を適用することが多いです。

配線幅と間隔をファイン化(微細化)すると歩留まりや信頼性が落ちやすいため、基板の価格が上昇します。このため、安定して作成できる「配線幅/間隔」と、価格が上昇するものの製造は可能であるという「配線幅/間隔」が存在します。

配線幅と間隔が小さくなれば、単位面積当たりに配線できる信号線が多くなり、基板面積を小さくしたり、配線層数を減らしたりすることができます。

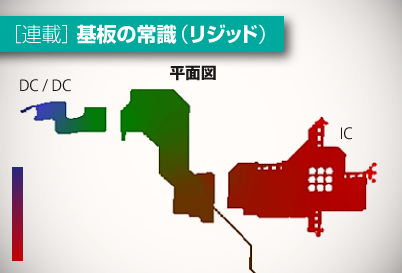

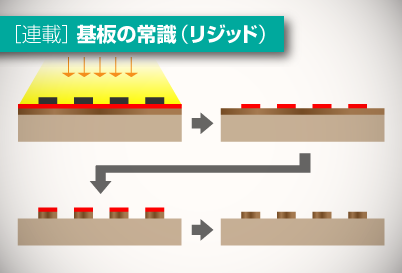

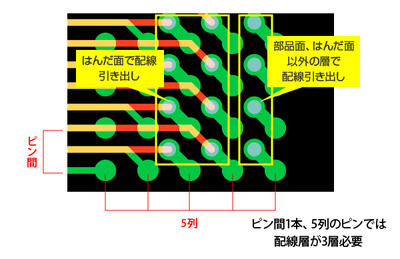

特にBGAなどの部品パッド間に何本の配線を通すことができるかは、配線層数を決定させる最大の要素となります(図1)。

もし、配線幅と間隔を大きくしても層数や基板面積を変わらずにすむなら、歩留まりや信頼性を高めるため大きくすることが望ましいです。

図1. ピン間配線本数と配線層数例

図1. ピン間配線本数と配線層数例

インピーダンス指定配線

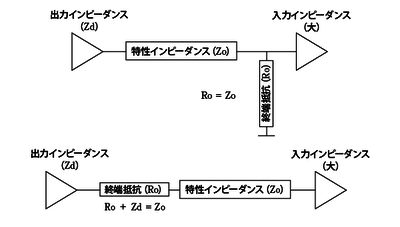

高速信号では、反射ノイズを抑えるために終端処理を行う必要があります。終端のインピーダンスと配線のインピーダンスを同じ値にするため、配線のインピーダンスをそろえます(図2)。

図2. 配線のインピーダンスと終端値

図2. 配線のインピーダンスと終端値

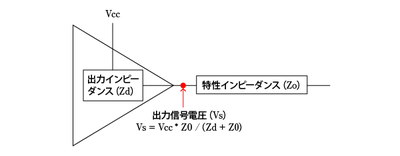

配線の特性インピーダンス(Zo)の値が低いと、信号の電圧が低くなります。これは信号の出力電圧はドライバの出力インピーダンス(Zd)と配線の特性インピーダンス(終端抵抗の値)との分圧になるからです(図3)。

図3. ドライバの出力信号電圧

図3. ドライバの出力信号電圧

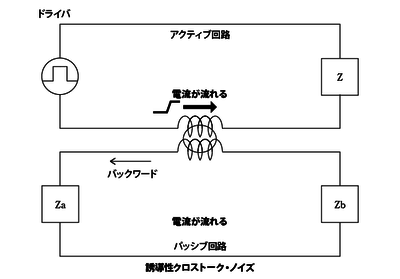

逆に値が高いと、クロストークノイズや電磁ノイズのような電流ノイズが発生するノイズ電圧が大きくなります(図4)。

図4. 電流によるノイズ

図4. 電流によるノイズ

このような理由と、基板で作りやすい配線幅と層厚の関係から、伝送線路の特性インピーダンスは50Ω、差動配線の差動インピーダンスは85~100Ωが一般に使われています。なお、PCI ExpressやUSBでは、規格の中に配線のインピーダンスが規定されています。

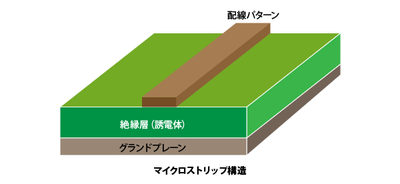

配線に安定した特性インピーダンスを持たせるためには、一般的に信号配線に隣接する層に広く安定した配線を施すマイクロストリップ構造を作ります(図5)。

図5. マイクロストリップ構造

図5. マイクロストリップ構造

積層基板で配線のインピーダンス制御が必要な場合は、グランド(G)や電源(P)を内層プレーン層とし、それに隣接する配線層で特性インピーダンスを持たせ、安定させます(図6)。

図6. 4層基板の層構成例

図6. 4層基板の層構成例

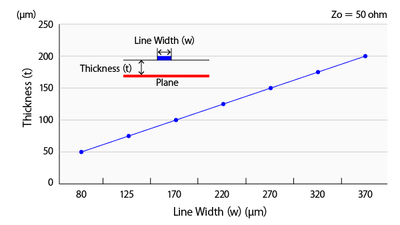

配線の特性インピーダンスは、信号配線とプレーン層の間に存在する誘電体の誘電率と厚さ、信号配線の幅に依存します。

これらの要素を使って配線の特性インピーダンスを計算するソフトを使用してインピーダンス配線幅を求めるのが一般的です。図7は、誘電体をFR-4とした場合で「配線の特性インピーダンスが50Ωになる層厚と配線幅の関係」を概算で示したものです。ただし、製造工場毎にインピーダンス配線幅は異なることもあるので、設計前に事前に確認することをお奨めします。

図7. 配線幅と層厚の関係(FR-4での概算値)

図7. 配線幅と層厚の関係(FR-4での概算値)

大電流配線

片面や両面基板は当然として、最近は多層基板でも配線で電源ラインを作成する場合が多くなっています。

これは、ICの電源電圧が多様化して1層や2層の電源プレーンだけでは全ての電源電圧に対応ができないためです。配線幅を決定する目安として、IPC-2152と呼ばれる規格があります。

IPC規格は、プリント回路協会(IPC:Institute for Printed Circuits)として発足したアメリカの規格で、世界各国の規格にも影響を与えています。現在は米国のエレクロトニクス接続協会(Association Connecting Electronics Industries)がIPCを制定しています。IPC規格には設計、製造、材料、フレキなど多くの規格があります。

IPC-2152では、基板配線に大電流を流すことで起こる熱に留意して、配線幅を決定するように求めています。

基板配線に使われる銅は銀と並んで常温で最も電気を通しやすい金属の1つですが、それでも小さな抵抗成分を持ちます。

導体の抵抗率をρ(Ω/m)、断面積をS(m2)、長さをL(m)とすると、配線の抵抗Rは、以下の式で求めることができます。

R=ρ×L/S

銅の抵抗率ρは0℃の時「1.55×10^-8 Ω/m」で、1℃温度が上昇すると「4.4/1000」抵抗も高くなります。

つまり温度がt℃の銅の抵抗ρは、ρ=1.55×(1+4.4×t/1000)×10^-8となります。

この式を使って銅箔厚35μm、パターン幅1mm、長さ100mmの配線の30℃での抵抗を計算すると、約50mΩとなります。

この配線が持つ抵抗成分は一般の信号配線では大きな問題にはなりませんが、大電流を流す電源配線では、2つの問題を引き起こします。

1つは配線による電圧降下の問題で、もう1つは配線からの発熱です。

電圧降下(DCドロップ)

どんなに小さな抵抗値でも大電流が流れると、電圧降下が無視できないほど大きくなります。例えば、配線の抵抗値が50mΩに20mAの電流が流れた場合では、配線による電圧降下は1mVですが、2Aの電流が流れると電圧降下は0.1Vと大きくなります。

10Vの電源ラインで0.1Vの電圧降下は1%、5Vでは2%ですが、1Vの電圧に対しては10%の電圧降下となります。

一般にICの電源電圧の許容誤差は5Vや3.3Vでは±10%程度ですが、電源電圧が低くなるにつれて、許容範囲は小さくなります。最近のLSIでは1.0V±3%や、0.8V±3%と小さくなっています(表1)。

| メモリ規格 | 電源電圧(V) | 許容誤差範囲(%) | 許容誤差範囲(mV) |

|---|---|---|---|

| DDR | 2.5 | 8.0 | 200 |

| DDR2 | 1.8 | 5.5 | 100 |

| DDR3 | 1.5 | 5.0 | 75 |

| DDR4 | 1.2 | 5.0 | 60 |

表1. DDRメモリの電源電圧と許容誤差範囲例

1.0V±3%や0.8V±3%が電源電圧のLSIでは、許容誤差は30mVや、24mV以内の変動誤差に抑えなくてはなりません。また、もしこれらのLSIが2Aの電力を消費するなら、電源配線の直流抵抗値は50%の余裕を見ると、6m~7mΩ以下にする必要があります。

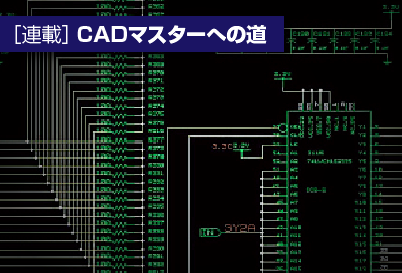

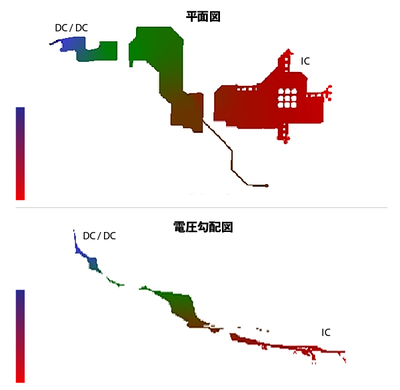

この電圧降下は電源品質(PI)解析の一分野とみられ、PIシミュレータには電圧降下の解析機能も有しています。それにより、複雑な形状の電源ラインでもDCドロップの大きさを検証することができます(図8)。

図8. PIシミュレータのDCドロップ解析(出典:HyperLynx PI、Mentor Graphics)

図8. PIシミュレータのDCドロップ解析(出典:HyperLynx PI、Mentor Graphics)

発熱による制限

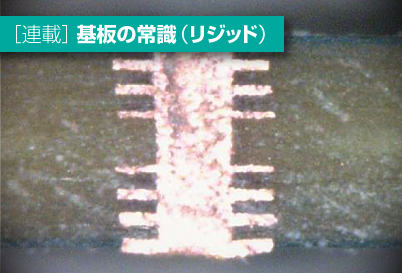

抵抗に電流が流れると電力が消費され、消費された電力は熱に変換します。配線での発熱は配線の温度上昇をもたらし、配線の抵抗率を上昇させ、さらに発熱させてしまいます。

配線の過剰な温度上昇は、断線や基板信頼性の低下につながるため、配線に流せる電流の容量には制限が生じます。

配線に流れる電流をI(A)、配線の抵抗をR(Ω)とすると、配線による消費電力Wは、以下の式で求めることができます。

W=V×I=R×I^2

配線からの発熱量は消費電力Wに比例します。配線の持つ抵抗値は配線の断面積に反比例し、配線の長さに比例します。同様に配線の放熱面積は、配線の長さに比例します。

このため、基板が広い空間に置かれた理想状態であれば、配線の発熱は配線の長さに関係なく、単位長さ当たりの直流抵抗に依存します。

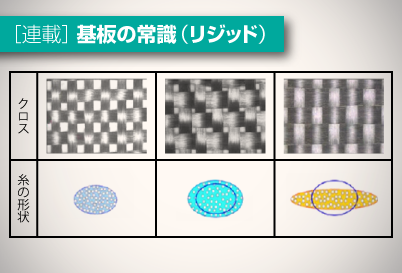

配線の発熱量と温度上昇の間には、基板材料の熱伝導率や周囲雰囲気の対流状況などいろいろな要素があり単純には決められませんが、大まかな設計目安を記載いたします。

銅箔厚=35μm、パターン幅1.0mmの時、配線の温度上昇(Δt)が10℃になる電流は約1.8A

この数値から安全を見込んで、銅箔厚=35μm、パターン幅1.0mmの配線での最大電流許容値は「1A」という値が経験値として使われています。

ビアについても許容できる最大電流容量は配線と同じく、穴の表面積と銅厚で配線の断面積が計算できます。

ビアの電流容量が不足する場合には、ビアを並列に複数配置したり、ビア内部に導体を充填したりして、電流容量を増やします。

配線抵抗を低減するには

配線に大電流を流すためには、配線の持つ直流抵抗を低減させることが必要です。

導線の抵抗Rは、先ほど紹介した通り「R=ρ・L/S」です。

配線を短くすると電圧降下を抑制できますが、(単位長さ当たりの)配線の発熱には効果がありません。

電圧降下にも発熱にも効果のある手法は、配線の断面積(S)を大きくすることです。断面積を大きくするには、配線幅を大きくするか銅箔厚みを厚くする方法があります。ここでは銅箔厚みについて記載します。

一般的な銅箔の厚さはメッキ厚を含め35μmです。ファイン配線やビルドアップ基板では18μmなどの薄い銅箔を、大電流を流す基板には70μmなどの厚い銅箔を使うこともあります。

同じ配線幅でも70μmの銅箔を使えば、断面積は通常の2倍になり、配線の持つ直流抵抗は半分になります。すると、流すことができる電流許容値は√2倍に増えます。

これは、配線からの発熱が配線の消費電力(W=V×I=R×I^2)に比例するためです。Rが1/2になれば、Iの限界は√2倍になります。また2倍の電流を流したい場合は、導体の断面積を4倍にするとよいでしょう。

これはある程度安全を見込んだ目安の値です。冷却や雰囲気の対流状況によって大きく値が異なるので、精度を上げるにはシミュレーションソフトを使ってください。

配線の断面積を大きくするには、配線幅を大きくする、あるいは配線の厚さを厚くするという点を覚えておきましょう。

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|