配置設計とフロアプランをCADでこなす

ICのピン数が増え、信号が高速化するに従って、フロアプランが必要不可欠になってきました。機能ブロックごとの基板設計だけではなく、大規模LSIなどの配置を検討して、伝送線路解析を進める必要があります。

フロアプラン、配置設計

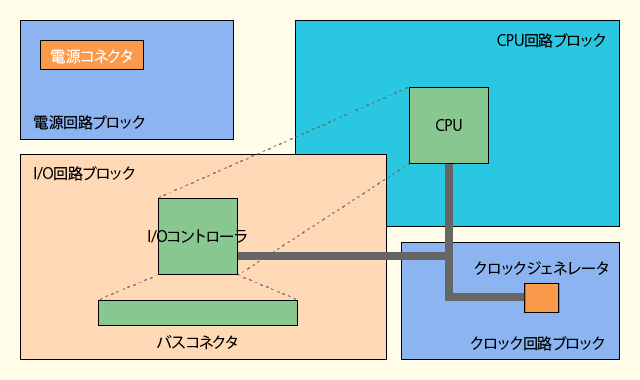

部品配置設計では、配置位置が事前に決まっている部品から手を付ける必要があります。ごく特殊な例を除いて、基板上にはコネクタやスイッチなど、配置位置を変更できない部品があります。部品配置設計では、これらの部品を基準に他の部品配置を設計していきます。

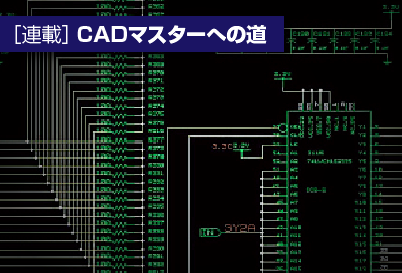

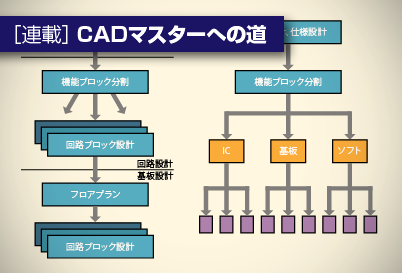

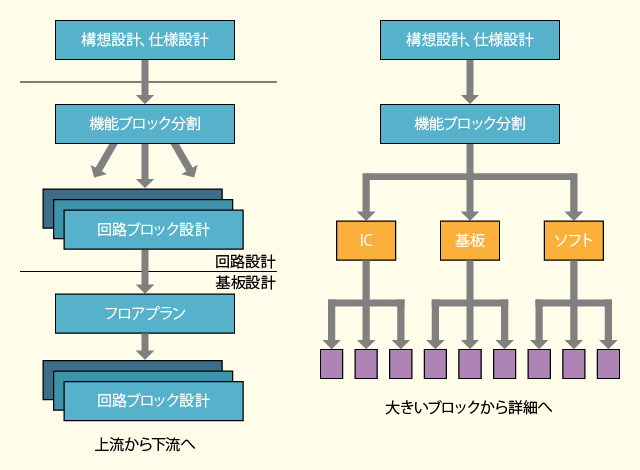

大規模な設計では、一度に全ての回路を設計することをしません。まず全体を幾つかの大きな機能ブロックに分割し、そのブロックをさらに幾つかに分割して、だんだん詳細な回路にまで、何段階かのブロック分けをします(図1)。

図1. 基板設計は機能ブロックで考える

図1. 基板設計は機能ブロックで考える

このようにすると、ブロック単位で複数の技術者に設計を振り分けることも簡単ですし、ブロック単位に設計を検証していくこともできます。このような大きな設計を徐々に小さく分割して行く設計を「トップダウン設計」と呼びます(図2)。

基板設計でもこの回路ブロックの情報が非常に役に立ちます。当然、同じ回路ブロック内の部品同士の配線は多く、ブロック間の配線はバスやクロック、ブロック間の情報や制御の信号に限られます。このため、部品の配置設計もブロック単位で行うとうまく効率的に進めることができます。

図2. トップダウン設計手法(大きいブロックから、段階を追って、詳細設計に進む)

図2. トップダウン設計手法(大きいブロックから、段階を追って、詳細設計に進む)

回路図番号で区別する

回路設計ではブロック内ごとに、部品へブロック名や回路図番号を付けておきましょう。CAD上で、どの部品がどの回路ブロックにある部品かが分かって便利です。ブロック名は回路図と基板上の部品を検索する時にも有効です。

コネクタをはじめとする配置が終わっている部品と、回路図のブロック接続図を使って、基板上でのおおよそのブロック配置を検討します。この時、あらかじめ基板の外側の余白にブロック単位で部品を配置しておくと、ブロックの大きさの見当がつきます。基板上では部品を両面に実装することが多いので、このことを考慮して大体のブロックの大きさを見積もる必要があります。

基板上にブロックを配置し、部品に付加されたブロック名と同じ名前を付けると、CADによっては部品配置設計や自動部品配置においてブロック単位での設計ができるような機能が用意されているものもあります。

ICのピン数が増えると同時に、信号の速度が高まるに従い、この「フロアプラン」が特別の役割を持つようになりました。

高速信号が存在する基板設計では、信号配線や部品配置に対して、設計上の制約条件が必要です。この制約条件の規定と基板設計への設定をフロアプランニングで行うと合理的です。この制約条件の決定と設定を目的とした、フロアプランニング用ツールが幾つか商品化されています。

フロアプランナー

高速信号を多く含んだASICや、ピン数の多い大規模LSIを組み合わせる基板設計では、フロアプランニング設計手法が有効です。

フロアプランとは、コネクタなど配置位置が決まっている部品と、部品の配置高さ条件を基に、ピン数の多い大規模LSIなどの機能ブロックの中心部品だけを配置し、配置の検討や伝送線路解析を行うものです。

フロアプラン手法は、当初、基本的な機能ブロック単位で部品の配置検討を行うためにIC設計で始まりました。基板の設計でも同様に部品配置の段階で一般に行われていて、特に「フロアプラン」などとも呼ばずに、特別な意識もなく、通常の部品配置の手法の一部としてとり入れられていました。

高速信号へどのように対応するか

高速信号では、信号の反射を避けるための終端技術が大切です。終端の課題は、通常、終端抵抗やダンピング抵抗を挿入することで解決します。しかし信号配線の長さによって、最適な終端方法や終端抵抗の値が異なることがよくあります。

加えて、高速なパラレルバス信号や差動信号では、信号間のタイミング同期が重要です。この信号の同期は主に、信号配線の長さを調整することによって制御します。

多くの場合、終端方法の設定や信号の同期については、基板設計にとり掛かる前に、伝送線路解析などによって設計規則化されています。そして制約条件として、基板設計に反映されます。

このような手順では、実際の基板設計前に制約条件を決めるので、実際の配線長さを反映できません。あらかじめ想定した配線長さを基に、ある程度の余裕を持たせて制約条件を決めます。

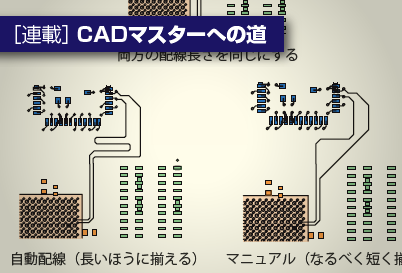

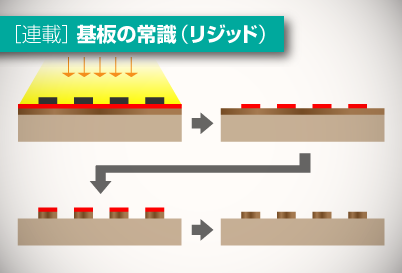

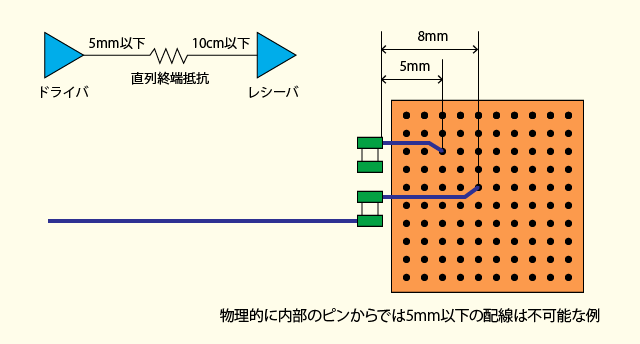

実際に基板設計を始めて、あらかじめ設定した配線長さより大幅に長くなったり、短くなってしまった場合、制約条件が変化する可能性があります(図3)。

図3. 想定した制約条件が実現不可能な場合もある(左上が制約条件)

図3. 想定した制約条件が実現不可能な場合もある(左上が制約条件)

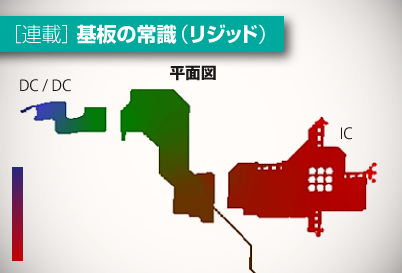

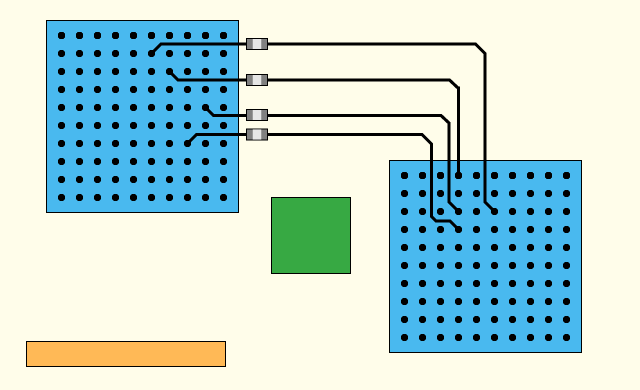

実際に部品を配置した段階ならば、配線の長さをおおよそ見積もることができます。この段階で実際の配線長さに即した解析を行い、制約条件を再設定すれば、より精度の高い制約条件が定まり、品質の高い基板設計が可能となります(図4)。

図4. 実レイアウトのデータから制約条件を作成すると精度が高い

図4. 実レイアウトのデータから制約条件を作成すると精度が高い

「フロアプランナー」は伝送線路シミュレータと、基板設計の簡易部品配置設計機能、簡易配線設計機能などを統合したツールです。主要部品を配置し、実際の配線に基づいた伝送線路解析ができるようになっています。

フロアプランナーの重要な機能は、伝送線路解析をしながらの配置検討と、制約条件の設定です。このため、制約条件の設定機能は特に使いやすく分かりやすい必要があります。この条件を満たす条件設定として、スプレッドシートを使った制約条件設定が多く使われています。

幾つかのハイエンド基板レイアウトシステムでは、特にフロアプラン専用のツールではなく、フロアプランニング機能が配置検討機能の一部としてサポートされています。

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。