配置が難しいLSI、どうするバス配線

ピン数の多いLSIを複数接続する際によく用いるバス配線は、比較的大きな面積を必要とします。そのため、配置層やLSIの向きなどを工夫してバス配線の交差やねじれを解消しつつ、他の信号線より優先して配置・配線をすることも少なくありません。中でも高速バスは、配線を同一層内に収めつつ等長配線が求められるなど、厳しい制約があります。

部品の配置層と配置方向

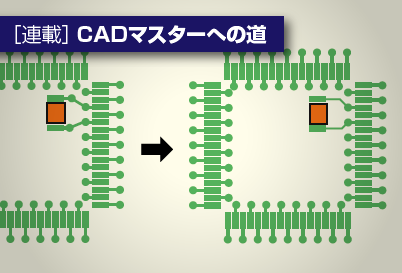

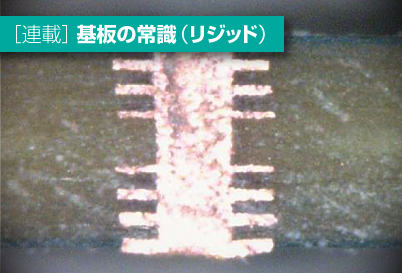

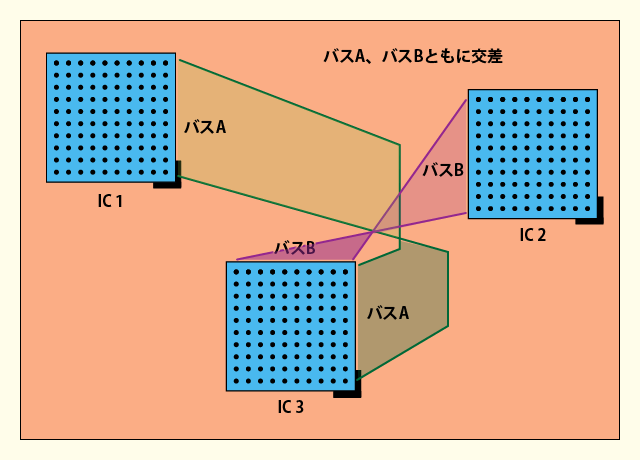

大規模LSIや多ピンコネクタなどは、ピン数が非常に多く、複数の異なるバス配線が接続されている場合も少なくありません。その場合、バス配線がねじれたり、相互に交差してしまうことがよくあります(図1)。

図1. 大規模LSIが複数あるとバス配線が交差する場合がある

図1. 大規模LSIが複数あるとバス配線が交差する場合がある

バス配線の交差は、ASICのようにピン配置を基板設計に合わせて変更できる場合は、避けることができます。また、汎用部品でも規格に合わせたり、チップセットのように組み合わせて使う場合は、最適に配線できるように決められています。デザインキットも、このような組み合わせのものは、よく提供されています。

しかし、決められた組み合わせ以外の汎用ICを使ったり、システムの仕様上、異なる部品を使う場合などは違います。全ての配線を交差せずに接続するよう、部品を配置することが難しいのです。それでも、多くの配線が交差しないように、問題を解決する必要があります。

バス配線が交差している場合、信号配線の層数が多ければ交差を避けることができます。また、同一バス内の配線が交差している場合でも、一部の信号が個々に交差している場合はさほど問題になりません。しかし、図1のように全体がねじれているような場合は、部品の向きや配置面を変更し、ねじれをなくす必要があります。

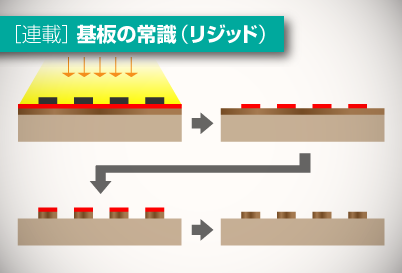

部品の配置面を変更すると部品のピン番号が反転し、信号のねじれが解消することがあります(図2)。また、配置方向を変更することで、ねじれや引き出し方向を解消できることもあります。

図2. はんだ面に部品を配置することで信号のねじれを解消できた例

図2. はんだ面に部品を配置することで信号のねじれを解消できた例

このようにしてバス配線を考えながら、配線層数やバス配線の制約条件を基に、部品の配置層や配置方向を調整し、キーパーツのおおよその配置を決めます。

なお、メモリに用いるDDRのような高速バス配線では、タイミングスキューに対する要求が厳しくなります。このような場合、バス配線内の全ての配線を同一層内に同じ長さで配線することが要求されることもあるため、配線のねじれは大問題となります。

バイパスコンデンサをどこに置くか

LSIの配置に関連して、バイパスコンデンサ(パスコン)や終端抵抗の配置、配置層の検討が必要になります。

バイパスコンデンサの配置は、一般にLSIの電源、グランドピンからの配線を最短にする必要があります。そのため、LSIの配置層の裏面に置き、基板の両側から、電源、グランドのプレーン層に接続します。

終端抵抗も多くの場合はLSIに近く、配線が短くなるように配置する必要があります。LSIと同じ層に配置して、無駄なビアを作らないようにします。LSIの配置検討には、周囲や裏面にこのような部品を配置するための領域も考えておく必要があります。

バス配線からの配置検討

パラレルバス配線の場合、全ての信号に対して配線長さの差を、ある範囲内に収めなければなりません。DDRほどではありませんが、部品の配置検討を進める場合には、バスや信号の交差だけではなく、バス信号の配線長を同じにすること、配線しやすくすることも必要です。

32ビットや64ビットといったビット数の多いバス配線では、BGAなどの部品の縁からピンまでの距離の差だけをとっても相当な長さの違いがあります。

等長配線では、最も長い配線に全ての配線長をそろえる必要があるため、短い配線はわざと配線を回り込ませて配線を長くします(図4)。同一バス内でピンからピンまでの距離の違いが大きいほど、配線長をそろえるための冗長配線が長く、配線領域が大きくなります。部品間が近く、配線の短いバスほど配線領域に余裕が少なく、冗長配線が困難になります。

図3. バス配線は広い領域を占有する

図3. バス配線は広い領域を占有する

領域内にビアなどを配置することは困難

32ビットや48ビットのバス配線は、非常に大きな配線領域を必要とします。ブラインドビアやベリードビアのようなIVH(非貫通ビアホール)を使わない場合、バス配線の領域には部品のスルーホールピンや表面実装部品からの配線引き出しビアを置くことは困難です。

例えば配線幅、配線間隔がともに150μmの場合、32ビットのバス配線を1つの層で配線すると、1cm近くの幅が必要になります。長さをそろえるために冗長配線する場合には、幅がさらに広くなります。

引き出し方向の検討が必要

バス配線を部品から引く場合、引き出し方向の検討も欠かせません。配線長をそろえたり、配線のねじれをなくすために、わざと最短ではない方向にバス配線を引き出す場合があります。異なるバスが交差する場合は、バスごとに異なる配線層を使う必要があります。しかし、異なるバスが、隣り合った層で長い距離を並行して走ると、クロストークノイズの発生する可能性があります。

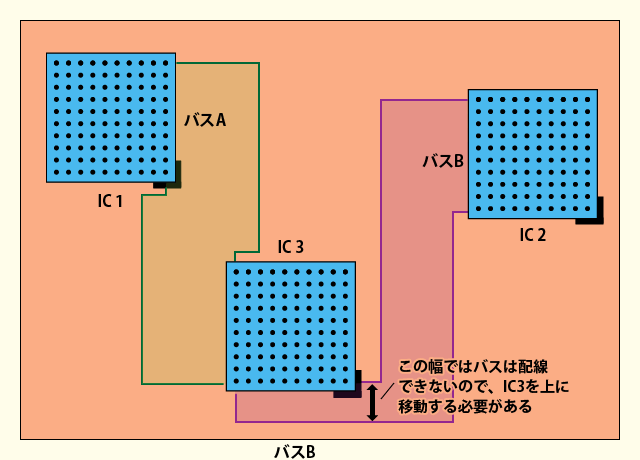

主要部品の配置がおおまかに決まった時点で、バス配線に必要な幅と配線層を決定して、バスの引き回しのおおまかな設計をすると同時に、主要部品配置の検証をします。

バスの引き回し検討で重要なことは、バスの配線長さに対する制約条件です。検討したバスの引き回しで、バスの配線長さ制限以内で配線が不可能であれば、バスの引き回しを変更したり、機能ブロックの配置や方向を変更する必要があります(図5)。

図4. バス配線では配線領域も考慮する

図4. バス配線では配線領域も考慮する

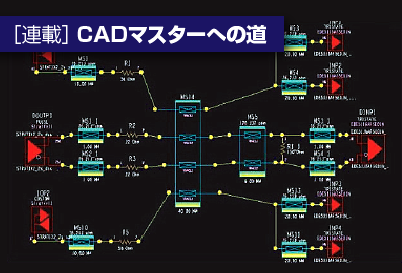

高速度信号基板設計

現在、PCI Expressをはじめとした高速シリアルリンクと呼ばれる信号は、1GHzを超えています。DDRなどのパラレルメモリバスの速度も1GHz動作を考慮することがあります。

これら高速信号では、これまで以上に基板設計が重要な役割を担います。配線が少しでも最適化から外れてしまっただけで、高速信号が正しく伝わらなくなるからです。

高速信号では、信号ごとのビアや部品パッドの特性(形状)が異なることで配線特性が変化し、信号が正しく伝わらなくなることがあります。特に、シリアルリンクで使われる差動信号は、+と-の信号ペアのタイミングスキューに対する要求が厳しく、配線遅延を同一にする必要があります。

このため、特定の信号にはビアを全く使わないか、使ったとしても1個だけにとどめるといった使用制限や並行配線を守ることなど、設計に対して厳しい要求が課せられることもあります。

これまでの設計では、ビアの形状(穴径、ランド径、内層のクリアランス径など)や、部品パッドの形状は、基板製造性から決められてきました。基板の製造歩留まりやはんだ付け歩留まりなどです。高速信号の場合は、配線の電気特性がなるべく均一になるような観点から、ビア形状や部品パッド形状を設計することも要求されるようになってきました。このような要求に応えるため、3次元のフィールドソルバーなどのシミュレーターを使います。

高速信号配線に対して、今までなかったような要求が今後は出てきますし、CADに対してもこれまでの高周波回路設計CADのような機能が求められるでしょう。

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。