未配線処理はマニュアルで対応

配線が完了した後は、ビアを削減したり、パターン整形が残っています。電源やグランドの配線には一般配線とは異なる課題があります。層の分割がおかしい、島ができている、特性インピーダンスの変化に対応していない。このような課題にもマニュアルで対応します。

クリーンアップ

配線が残り少なくなってきた時の配線設計では、手間と時間がかかります。これらの配線はマニュアルで配線しなければなりません。ラッツネスト表示を見ながら、配線できそうな経路を探していきます。多層基板では一層ずつ配線を表示して、この層でここまで、次の層ではここまで、などと大体の道筋を考え、その後、実際の配線設計に入ります。

あらかじめ配線してあった制約条件の付いたクリティカルネットを変更しなければならない場合もあります。このような配線を操作するときには、配線の制約条件をよく考慮して、エラーが発生しないように注意します。必要であれば終端抵抗やバイパスコンデンサなど、電気特性に影響しない範囲で多少場所を移動させたり、配線引き出しビアの位置を動かす場合もあります。

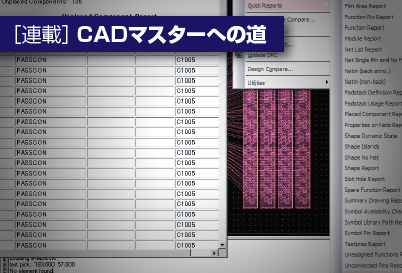

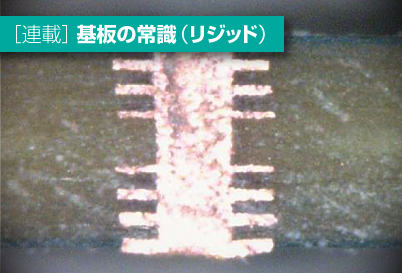

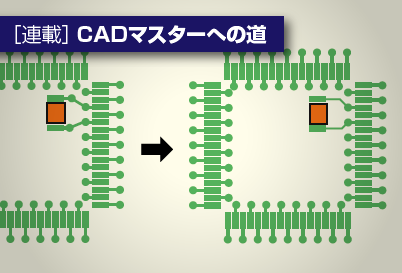

ピンからの引き出しパターンのうち、配線がない無駄な配線引き出しビアを削除し、他の層に配線が通れるようにすることもあります(図1)。いろいろ工夫して配線を通すスペースを空け、必要な配線を全て完了させます。

図1. 無駄なビアの削除

図1. 無駄なビアの削除

生産性や品質を考える

全ての信号の配線が終わって、エラーがなくなれば、基板の必要条件が満たされます。しかし、これで設計が終わるわけではありません。まず、基板の生産性や品質を上げるため、配線設計の整形処理を施します。

多層基板で配線を完成させるためにビアはなくてはならないものですが、同時に基板製造時の不具合の原因になることや、配線の電気特性を落とす原因でもあります。ビアの数を減らすことは基板製造コストからも、電気特性からも大変有利になります。

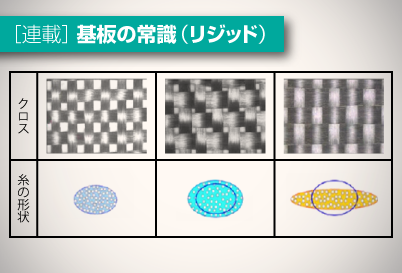

ビア以外にも配線の整形にはいろいろあります。配線の角を90度から45度に変更したり、配線の不自然な回り込みをなくしたり、配線長さを短くしたり、配線やビア、パッドのクリアランスを広くしたりする処理です。いずれも、基板製造の歩留まりを高めると同時にクロストークノイズの減少や基板の電気特性の向上にもつながります。

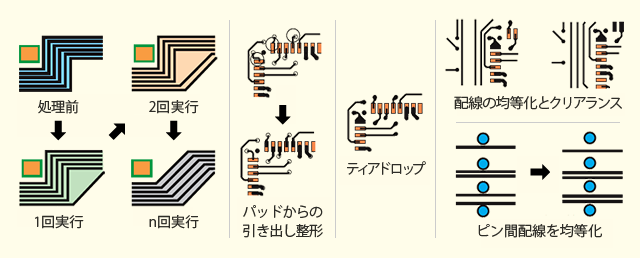

配線パターン整形は、未配線修正時やそのつど気がついたときにマニュアルで進めます。自動整形機能も多くのCADでサポートされており、どの機能を使うか、何度行うかなどのパラメータで動作をコントロールできます。通常、このような処理は1回実行しただけでは十分な効果が得られないので、処理を組み合わせて、何回か繰り返し処理をします(図2)。

自動整形処理の実行に際しては、制約条件付きの配線に対して配線を変えないように、「変更不可」指定が設定されていることを忘れずに確認しておきます。

図2. 代表的なクリーンアップ例

図2. 代表的なクリーンアップ例

電源ラインの配線

現在、電源やグランドを大きくとる基板は4層以上で配線、電源やグランドはプレーン層はプレーン層を使用することが多いです。これは、高速信号配線の特性インピーダンスを安定させたり、同時スイッチングノイズ(SSN)を低下させるために必要な工夫です。

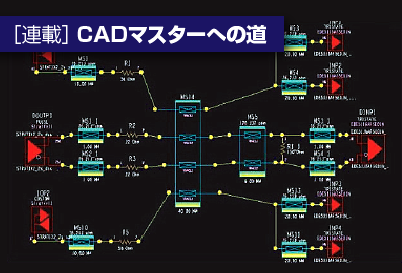

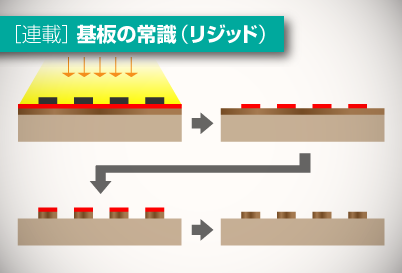

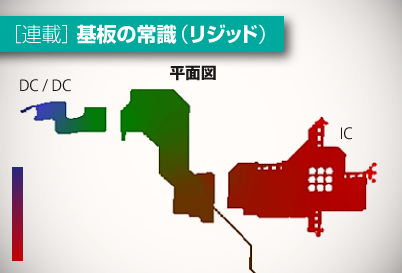

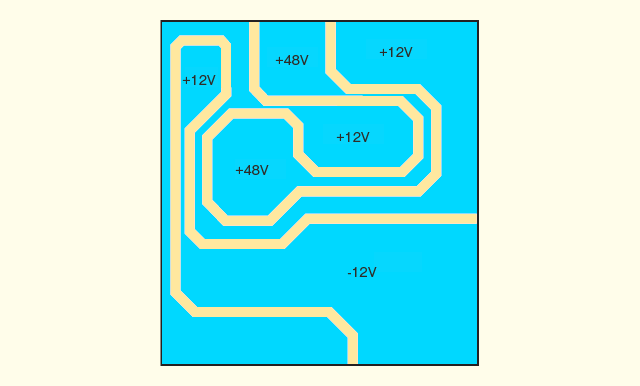

プレーン層の設計は、一般の信号配線とは異なります。禁止領域や基板周辺部のクリアランスを設定するだけで、プレーンの電源層やグランド層を比較的簡単に作成できます。ただし、1つのプレーン層に2つ以上の電源信号やグランド信号が存在する場合の電源層分割では、層の分割に注意が必要です(図3)。部品の配置が悪いことで、1カ所だけ電源ピンを他から離れたところに置いたり、バイパスコンデンサの位置が適当でなかったりといった配置のエラーをこの時点で発見することもあります。

分割されたプレーン層を作成する時、同じ信号が離れた場所にあるとき、どのようにこの離れた場所を1つのプレーンとして作成すればよいのでしょうか。あるプレーンが他のプレーンの接続のじゃまをしないようにする他、プレーンの細くなる箇所が出ないように注意します。

図3. 電源層の複雑な内層分割

図3. 電源層の複雑な内層分割

分かりにくい「境界」や「島」

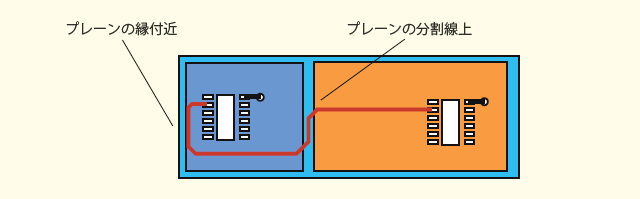

特性インピーダンスは、基準となるプレーン層が分割されてるといると変化します。反射ノイズの発生原因になりますから、プレーンの分割部に隣の層の高速信号が通らないようにします(図4)。

図4. 特性インピーダンスが変化しやすい場所

図4. 特性インピーダンスが変化しやすい場所

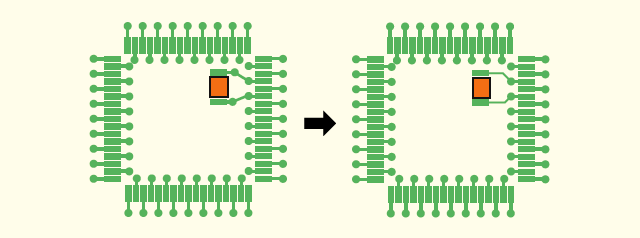

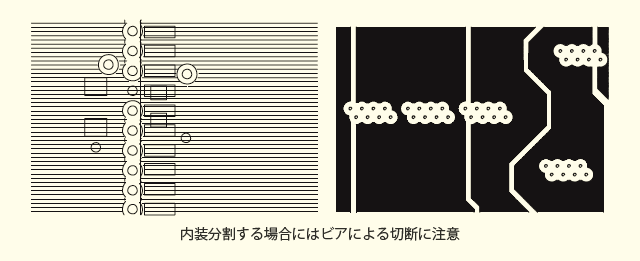

分割プレーンだけではなく、全面プレーン層でも起こる問題があります。BGAやQFPのLSI、高密度コネクタ周りでは、密集したピンやビアのクリアランスが影響し、プレーン層の接続が非常に細くなったり、全く信号接続のない”島”と呼ばれる浮いた領域ができてしまうことがあります(図5)。島はノイズの発生源にもなりますし、素子に電源やグランドが接続されない原因にもなります。

図5. 内層分割する場合にはビアによる切断に注意

図5. 内層分割する場合にはビアによる切断に注意

多くの電源、グランド信号が存在する基板では、それらの全てをプレーン層で接続するのではなく、信号層を使って配線する場合もあります。EMC対策や基板製造上の問題から、配線層の空白部をグランド面で全て覆うことがよくあります。グランドの面パターンは、基板の放熱設計のためにも有効です。このような電源やグランドの太い配線や面パターン作成のために、専用の機能が用意されている場合もあります。

なお電源配線を太い配線で引く場合は、大きなスペースが必要ですが、クリティカル配線や一般信号を配線するスペースを確保する必要もあります。後から太い配線を引くのではなく、あらかじめスペースを確保しておきましょう。

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。