協調設計と伝送線路シミュレーション

協調設計(コンカレントエンジニアリング)を採用しないと基板が設計できない場合が増えてきました。ICベンダーが提供するデザインキットも協調設計の下敷きとして使うことができます。伝送線路シミュレーションを実行するタイミングは、回路設計から基板設計に至る3つの段階にあり、ここでも協調設計が有用です。

協調設計

多くのシステムにはASICが使われています。ASICは汎用ICとは違い、ユーザーが仕様を決めるため、設計に自由度があります。これまで、基板設計者にとってこのような自由度はあまり関係がありませんでした。IC設計者と基板設計者は会社や部門も異なり、完全にそれぞれ独立して設計していたからです。

しかし、ICのピン数が多くなり、信号が速くなってくると、基板設計を含めて、ASICの設計自由度を可能な限り利用しないと、最適設計が困難になってきました。

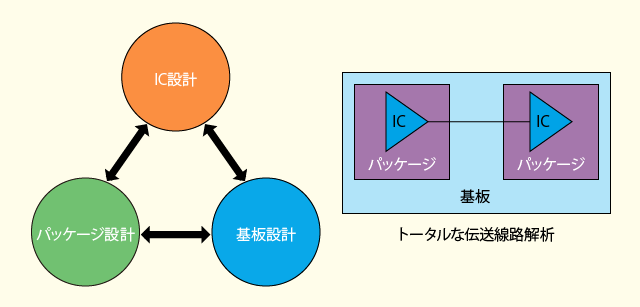

IC設計とICパッケージ設計、基板設計の三者が協調して最適設計を行うことで、最適なシステム設計が可能となります。三者が協調して、システム開発を行うことを「コンカレントエンジニアリング」や「協調設計」と呼びます。

ASICではドライバの強さ(駆動能力)が何種類か用意されており、基板設計の状況に応じ、最適なドライブ能力を選択できます。この結果、基板の終端設計が楽になると同時に、信号の波形歪みの小さい、品質の高い基板設計が可能となります。

DDR2メモリをはじめとして、ICの中には、レシーバに終端抵抗回路が付加できるようになっているものもあります。ICの内部に終端抵抗を付加することにより、基板設計が楽になると同時に、レシーバに最も近い最適な場所に終端を付加することができます。

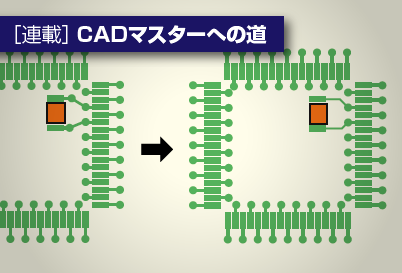

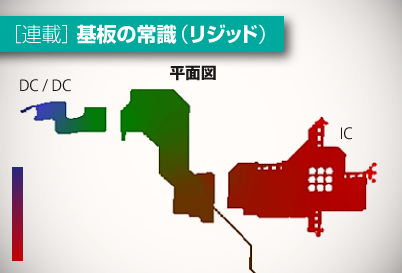

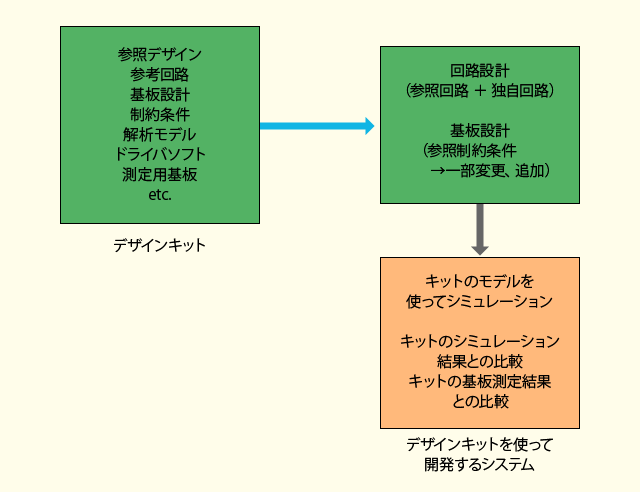

ICのドライブ能力、終端抵抗の値を高い精度で定めるには、基板とパッケージ、ICの協調設計を進め、全てを含んだ伝送線路解析を行います(図1)。

図1. 協調設計の考え方

図1. 協調設計の考え方

ピン割り付けを最適化しやすい

ICとパッケージ、基板を協調設計するもう1つのメリットとして「ピン割り付けの最適化」があります。

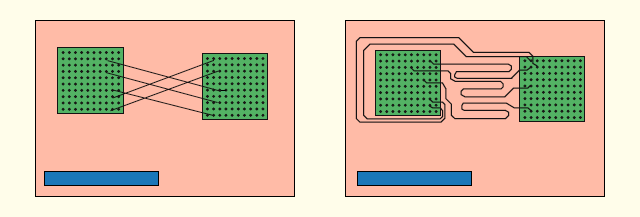

ピン数の多いLSIを使った基板では、LSIからの配線の引き出し設計が非常に困難です。信号配線の交差を防ぐため、ASICからコネクタや汎用ICなどに配線するとき、配線にビアを使ったり、配線を回り込ませたりします。この結果、配線が長くなったり、多くの配線層が必要になったりします(図2)。

図2. 配線に交差があると等配線長のバス配線が困難で品質は悪い

図2. 配線に交差があると等配線長のバス配線が困難で品質は悪い

配線が長くなったり、多くのビアを使うと、信号の品質も悪くなります。

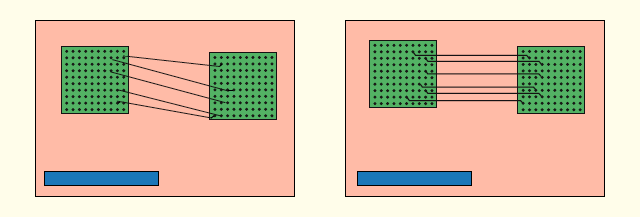

ICのパッドの割り付けやパッケージの設計を工夫し、基板上で配線が交差しないようにピンを配置すれば、基板の設計は楽になります。同時に基板の品質も大幅に向上します(図3)。

図3. パッケージのピン配列を変えて交差がなくなると基板品質は大きく向上する

図3. パッケージのピン配列を変えて交差がなくなると基板品質は大きく向上する

ICの消費電力が増大し、信号が高速化すると、同時スイッチング(SSO)ノイズが増大します。SSOノイズを小さくするため、ICのパッケージやICチップではできるだけ電源ピンやグランドピンを多く配置し、電源とグランドの供給ラインを増やします。加えてパッケージやICチップの上にバイパスコンデンサ(パスコン)を付けます。

コンカレントエンジニアリングでは、基板上のパスコンの効果や、パッケージのグランドピン、電源ピンの最適化を図ることもできます。

伝送線路シミュレータ

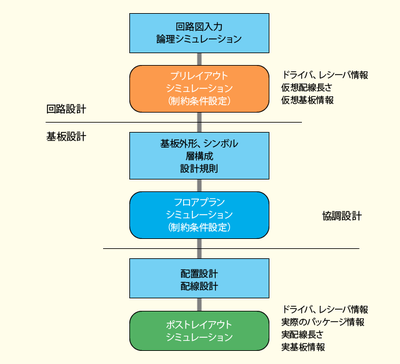

現在、伝送線路解析は基板設計に欠かせないツールです。伝送線路解析を実行するタイミングは、基板設計の流れの中で3つあります(図4)。

図4. 伝送線路解析の実行タイミング

図4. 伝送線路解析の実行タイミング

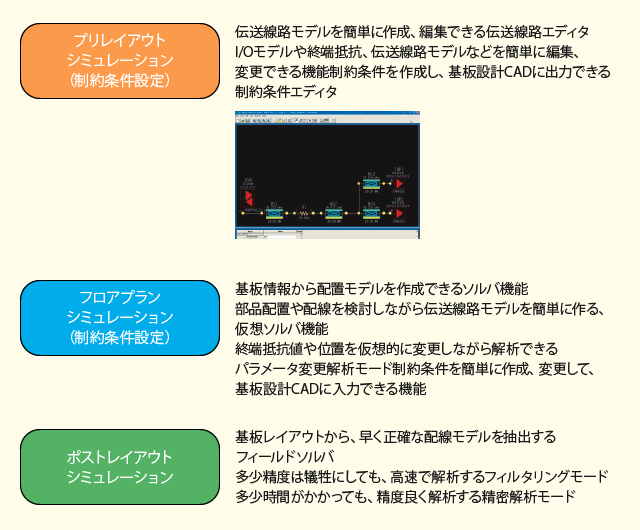

第1は基板設計が始まる前の「プリレイアウトシミュレーション」。制約条件設定のために実行します。基板が設計されていませんから、大体の配線長さを想定して解析します。ここで、配線の長さ制限や終端抵抗、ダンピング抵抗の大きさと挿入位置など、基板設計の制約条件を設定します。

プリレイアウト解析では、実際の配線がないので、シミュレータ上で配線の条件やトポロジーを自由に設定できなければなりません。

このため、伝送線路エディタ機能が必須になります(図5)。配線長さや終端抵抗値などを簡単に自由に変更できる必要もあります。プリレイアウトシミュレータでは、制約条件エディタも重要な機能です。

図5. 各シミュレーションに必要な機能

図5. 各シミュレーションに必要な機能

解析を行う第2のタイミングは、フロアプランニングです。現在、フロアプランニングの主目的は解析です。伝送線路解析機能をもたないフロアプランニングは、フロアプランニングとは呼ばないようになっています。

フロアプランニングでは、コンカレントエンジニアリングが有効な手法になっており、解析を実行するには、ドライバからレシーバまでの全経路について、トータルな信号の流れについて伝送線路解析を行う必要があります。「ICドライバ→パッケージ→ピン」や「ソケット→基板→ピン」や「ソケット→パッケージ→ICレシーバ」という経路です。

場合によっては、メモリモジュールなどのように、コネクタを介して複数の基板にわたる信号の解析も要求されます。フロアプランニングでの解析の際、階層解析の機能があると、コンカレントエンジニアリングを有利に進めることができます。

基板設計が終わった段階で解析する

第3の解析タイミングは、基板設計が終わった段階です。設計品質確認のための解析です。

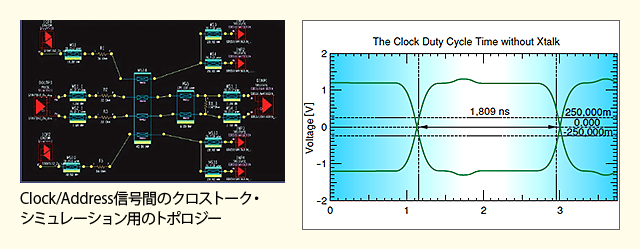

この段階では、基板の配線設計は全て終わっていますから、実際の基板設計に従った正確なSI(シグナルインテグリティ)解析が実行できます。設計が終わった後の解析なので、「ポストレイアウトシミュレーション」と呼ばれます。

全ての配線をバッチでチェックすることにより、当初設定していたクリティカル信号以外の配線やクロストークノイズで思いがけないクリティカルネットを発見することもあります。

ポストレイアウトシミュレーションでは、基板の配線状態を正確にシミュレーションの配線モデルに組み入れるため、基板の配線を正確に読みとって伝送線路モデルに変換するためのフィールドソルバが必要です。さらに、高速に多くのネットを解析してクリティカルネットを発見するフィルタリング解析と、クリティカルネットを正確に解析する詳細解析の2つのモードが必要となります。

デザインキット

現在、基板の設計は大変難しくなっています。ICの集積度が高くなり、ピン数が多く、信号が非常に高速になると同時に、ICの消費電力も大幅に増加しているためです。

このため、基板設計者や回路設計者は高速信号配線だけではなく、ICの発熱やヒートシンクの設計、同時スイッチングノイズを防ぐためのバイパスコンデンサの配置と配線まで、非常に多くの矛盾する要素を考慮しながら設計を行う必要があります。

基板のコストを上げずに、これらの矛盾を整えバランスをとって解決することが非常に困難になってきました。場合によっては、コストを下げるために、ICの性能を抑えて使わなければならないこともあります。ICの動作速度を低くすれば、伝送線路上の設計は楽になりますし、ICの発熱も低く抑えることができます。しかし、わざわざICの性能を抑えて使用するならば、もっと安い低性能のICを使うことと変わりません。

あまりにも実装設計が難しいと、せっかくICが良い性能を持っており、価格が安くても、ICの性能を生かすための基板のコストが上がってしまいます。ICの競争力の低下です。極端に言えば、基板の設計ができなければ、そのICは使えません。

デザインキットを利用して設計する

ICベンダーは、基板上で自社のICが性能を発揮できるよう、EDAベンダーと協力して、ICデザインキットを提供しています。

ICデザインキットには、論理シミュレーションモデルや伝送線路解析モデルなどいろいろな構成があります。

ここでは、基板設計用のモデルの代表的な構成について、デザインキットを見てみましょう。

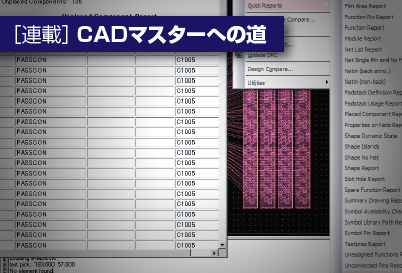

代表的なデザインキットにはリファレンスモデルとして、そのICを使った回路設計と基板設計、制約条件、伝送線路モデルと解析結果などが含まれています。ユーザーはデザインキットを使い、レファレンスモデルの制約条件をもとに、考案した回路を用いた基板を設計します(図6)。

図6. デザインキットの利用

図6. デザインキットの利用

設計結果は、キットに含まれているシミュレーションモデルを使って解析できますし、キットに含まれている解析結果との比較で、簡単に良しあしが判断できるようになっています。

デザインキットによっては、実際の基板が含まれていて、信号の波形観測までできるようになっているものもあります(図7)。

デザインキットは基板設計の手本とガイドラインです。設計が簡単になったり、シミュレーションモデルが簡単に収集できるなどのメリットがあります。

図7. DDR2デザインキットの一例

図7. DDR2デザインキットの一例

| < 前の記事 | 記事一覧 | 次の記事 > |

|---|

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。

本記事は、「Allegroで学ぶ実践プリント配線板設計」(発行元:株式会社ジー・ビー)から一部転載しています。